### Von Neumann architecture

11.1A Computer systems

### Lerning objectives

- •describe the interaction of CPU with peripheral devices

- •describe the purpose of CPU components, system bus and main memory

#### ASSESSMENT CRITERIA

- Describe the functions of CU, ALU

- Describe the pupose of system bus

- Describe the process Fetch execute decode cycle

### **Key Words**

| Control bus | is used to provide control signals to most parts of a computer system. |

|-------------|------------------------------------------------------------------------|

| Address bus | is used to address the main system memory                              |

| Data bus    | Is used to transfer data                                               |

| Peripherals | devices that can be easily removed and plugged into a computer system. |

#### Dedicated registers

**Memory Address Register (MAR)** – The address in main memory that we wish to fetch the instruction from

**Memory Buffer Register (MBR)** – Holds the instruction that has been fetched from memory

**Current instruction register (CIR)** – Holds the contents of MBR, which is the in struction to be processed

**Program Counter (PC)** – This holds the memory address of the location to fetch the next instruction from.

**Status Register (SR)** – Gives information on such things as overflow/underflow, interrupts, parity. The status register allows an instruction to depend the outcome of the previous instruction.

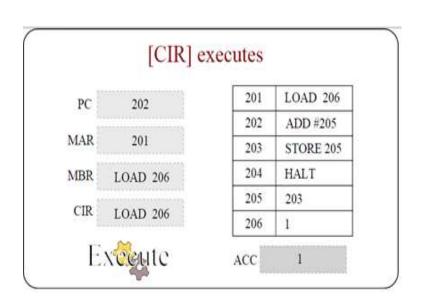

**Accumulator** – Holds the results of arithmetic and logic computations

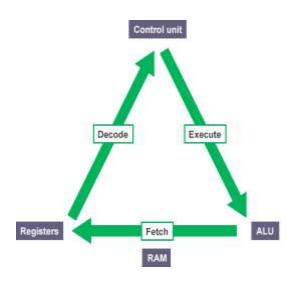

#### Fetch-decode-execute

https://www.youtube.com/watch?v=5s-faIDZI64&ab\_channel=SENIOR.PR OFESSOR

#### Register transfer notation

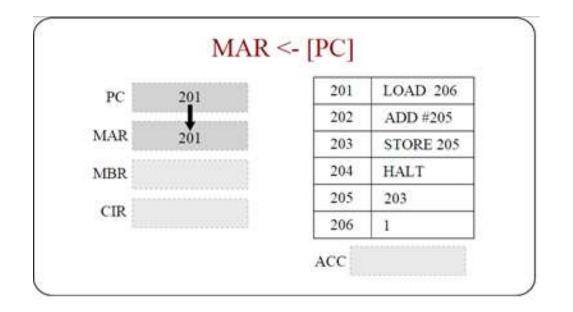

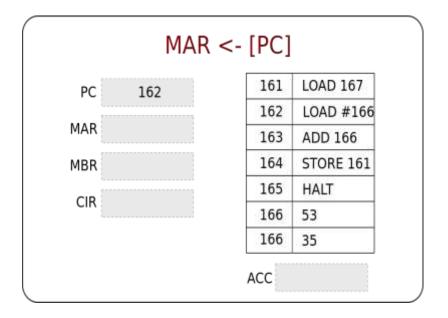

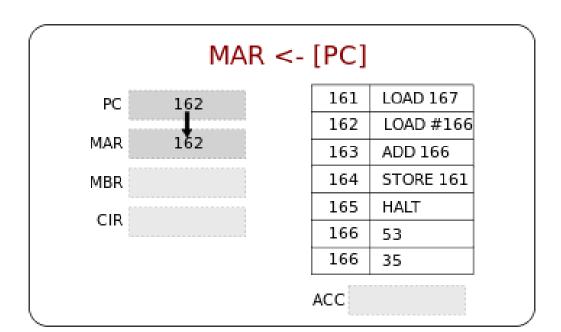

- 1. [MAR]  $\leftarrow$  [PC]

- 2. PC ← [PC] + 1

- 3. MDR  $\leftarrow$  [[MAR]]

- 4. CIR  $\leftarrow$  [MDR]

- DECODE

- 6. EXECUTE

- 7. GO TO STEP 1

#### Fetch-decode-execute cycle

The instructions are loaded into memory

The processor fetches the instruction from the main memory

The instruction is decoded so the CPU knows what to do with the instruction

The processor then decodes and executes the instruction

The result of the instruction can be stored in memory

The next instruction is then fetched from main memory and the cycle repeats itself

## **Fetch**

#### **Processor**

| Register | Content |

|----------|---------|

| PC       | 0       |

| MAR      |         |

| MBR      |         |

| CIR      |         |

#### Main memory

| Address | Content  |

|---------|----------|

| 0       | 00101001 |

| 1       | 11101010 |

| 2       | 11100101 |

| 3       | 10101110 |

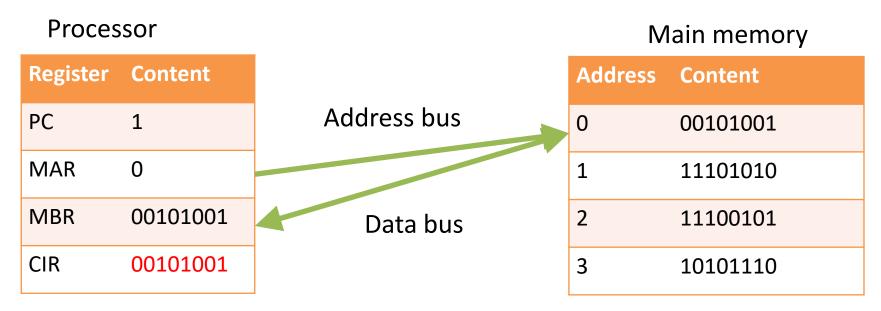

## Fetch: MAR $\leftarrow$ [PC]

| Proces   | sor     |             | V       | lain memory |

|----------|---------|-------------|---------|-------------|

| Register | Content |             | Address | Content     |

| PC       | 0       | Address bus | 0       | 00101001    |

| MAR      | 0       |             | 1       | 11101010    |

| MBR      |         |             | 2       | 11100101    |

| CIR      |         |             | 3       | 10101110    |

- Transfer the contents of the PC to the MAR

- The address in MAR is transferred to main memory along the address bus

Fetch:

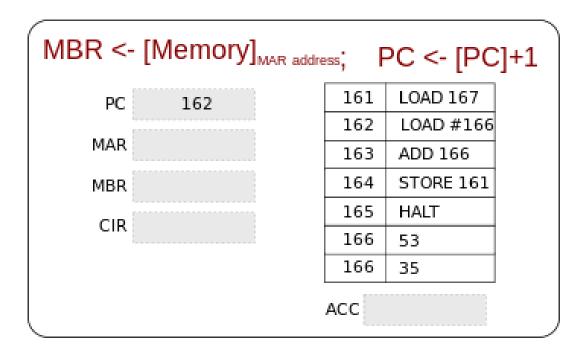

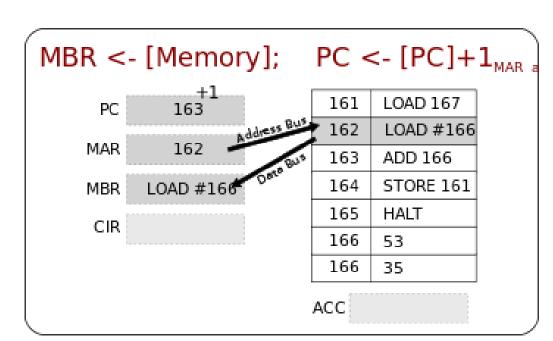

$$MBR \leftarrow [Memory]_{MAR \text{ address}}$$

;  $PC \leftarrow [PC] + 1$

| Proces   | sor      |             | M       | lain memory |

|----------|----------|-------------|---------|-------------|

| Register | Content  |             | Address | Content     |

| PC       | 1        | Address bus | 0       | 00101001    |

| MAR      | 0        |             | 1       | 11101010    |

| MBR      | 00101001 | Data bus    | 2       | 11100101    |

| CIR      |          |             | 3       | 10101110    |

- The contents at that address is transferred back to the MBR along the data bus

- At the same time the PC is incremented by one to get ready for the next cycle. This can be done because the two steps do not rely on one another.

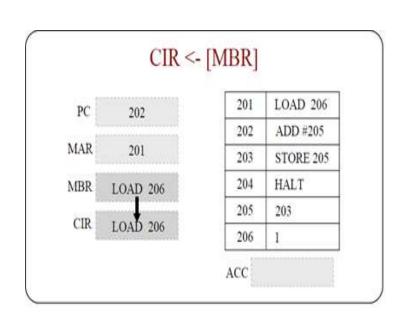

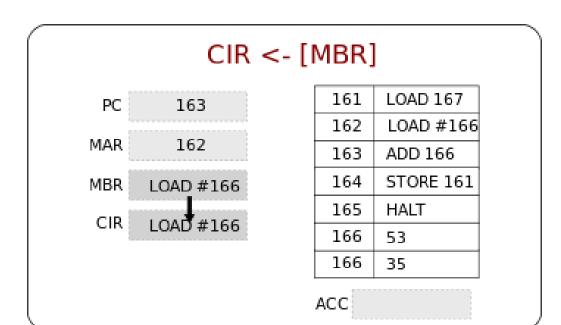

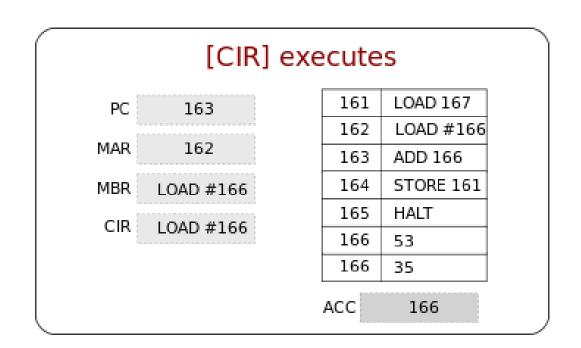

### Fetch: $CIR \leftarrow [MBR]$

- Transfer the contents of the MAR to the CIR ready to be decoded.

- This allows the MBR to be used to store the next instruction during the decode and execution stages.

#### Step by step description of fetch-execut-cycle

1. COPY THE ADDRESS THAT IS IN PROGRAM COUNTER(PC)INTO THE MEMORY ADDRESS REGISTER (MAR)

- 2. INCREMENT THE PC (READY FOR NEXT FETCH)

- 3. LOAD THE INSTRUCTION THAT IS IN THE MEMORY ADDRESS GIVEN BY THE MAR INTO THE MEMORY DATA REGISTER (MDR)

4. THE MBR LOADS THE CURRENT INS TRUCTION REGISTER WITH THE INSTRUCTION TO BE EXECUTED.

## **Activity**

Complete the following diagrams showing each step of the fetch decode execute cycle:

Continue till 165

## **A Level questions**

(b) The sequence of operations shows, in register transfer notation, the fetch stage of the fetchexecute cycle.

```

1 MAR ← [PC]

2 PC ← [PC] + 1

3 MDR ← [[MAR]]

4 CIR ← [MDR]

```

- · [register] denotes contents of the specified register or memory location

- step 1 above is read as "the contents of the Program Counter are copied to the Memory Address Register"

| (i) | Describe what is happening at step 2. |

|-----|---------------------------------------|

|     |                                       |

|     |                                       |

| ii) | Describe what is happening at step 3. |

|     |                                       |

|     |                                       |

# A Level questions

| (iii) | Des | cribe what is happening at step 4.     |

|-------|-----|----------------------------------------|

|       |     |                                        |

|       |     | [1]                                    |

|       |     |                                        |

|       |     |                                        |

| (d)   | (i) | Explain what is meant by an interrupt. |

|       |     |                                        |

|       |     |                                        |

|       |     |                                        |

|       |     | to to                                  |

## **A Level questions**

| ii) | Explain the actions of the processor when an interrupt is detected. |

|-----|---------------------------------------------------------------------|

|     |                                                                     |

|     |                                                                     |

|     |                                                                     |

|     |                                                                     |

|     |                                                                     |

|     |                                                                     |

|     |                                                                     |

|     |                                                                     |

|     | [4]                                                                 |

### **Answers**

| b) | (i)   | the program counter is incremented                                                              | [1] |

|----|-------|-------------------------------------------------------------------------------------------------|-----|

|    | (ii)  | the data stored at the address held in MAR is copied into the MDR                               | [1] |

|    | (iii) | the contents of the Memory Data Register is <u>copied</u> into the Current Instruction Register | [1] |

| d) | (i)   | a signal     from a device/program that it requires attention from the processor                | [2] |

|    | (ii)  | at a point during the fetch-execute cycle     check for interrupt                               |     |

|    |       | if an interrupt flag is set/ bit set in interrupt register                                      |     |

|    |       | <ul> <li>all contents of registers are saved</li> </ul>                                         |     |

|    |       | <ul> <li>PC loaded with address of interrupt service routine</li> </ul>                         | [4] |

|                  | 10101000                                                                                                                            | 10101  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------|--------|

| 101 <sup>3</sup> | A processor has one general purpose register, the Accumulator (ACC), and several special purpose registers.                         |        |

|                  | (a) Complete the following description of the role of the registers in the fetch-execute cycle by<br>writing the missing registers. |        |

|                  | The                                                                                                                                 |        |

|                  | The holds the data fetched from this address.                                                                                       |        |

|                  | This data is sent to the                                                                                                            |        |

|                  | The is incremented. [5]                                                                                                             |        |

|                  |                                                                                                                                     | 101000 |

|                  |                                                                                                                                     |        |

|                  |                                                                                                                                     |        |

| Question | Answer                                                                                                                                                                                                                                                                                                                                                                                      | Marks |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 3(a)     | 1 mark for each completed statement  The Program Counter holds the address of the next instruction to be loaded. This address is sent to the Memory Address Register.  The Memory Data Register holds the data fetched from this address. This data is sent to the Current Instruction Register and the Control Unit decodes the instruction's opcode.  The Program Counter is incremented. | 5     |

Work with pastpaper

### Lesson Feedback

3

3 things you have learned today 2

2 things were interesting for you 1

1 thing I want to learn more